네패스라웨가 첨단 팬아웃 패키징에 꼭 필요한 폴리이미드(PI)를 대체할 수 있는 기술을 개발했다. 업계 최초 성과로 고가의 PI이 없이 기존 방식으로도 첨단 패키징을 구현할 수 있게 됐다. 네패스라웨는 네패스의 패키징 전문 자회사다.

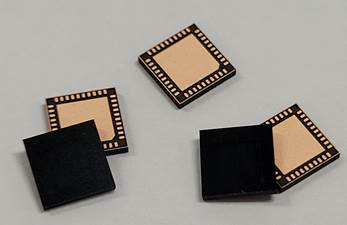

네패스라웨는 기존 몰딩 공법만으로 팬아웃-패널레벨패키지(FO-PLP)를 구현했다고 14일 밝혔다. 이를 반도체 칩으로 구현, 미국 아날로그 및 차량용 반도체 전문 기업에 샘플을 공급하기 시작했다. FO-PLP는 차세대 패키징 기술 중 하나로 네패스는 세계 최초로 전력관리반도체(PMIC)를 FO-PLP로 양산한 기업이다.

팬아웃(FO)은 반도체 입출력(I/O)을 칩 바깥에 배치해 그 수를 늘리는 기술이다. 칩 성능과 열 효율성을 높이는데 유리하다. 패널레벨패키징(PLP)은 둥근 웨이퍼 대신 사각 패널에 칩을 연결, 패키징 하는 것으로 테두리를 버리지 않아 한번에 많은 칩을 양산할 수 있다.

지금까지 FO-PLP 공정을 구현하려면 PI가 반드시 필요했다. PI는 가격이 비싸 다양한 제품에 활용하는데 제한적이다. 네패스라웨가 PI 대체 공법을 개발하게 된 배경이다. 네패스라웨가 구현한 공법은 QFN과 같은 기존 몰딩 패키징 기술로 FO-PLP를 구현, 공정을 단순화하고 생산성을 높일 수 있다.

특히 다양한 제품을 수시로 변경하고 개발해야하는 아날로그 반도체 제조사는 인쇄회로기판(PCB) 및 리드 프레임 등의 재료 수급 위험을 줄일 수 있다. 기존 반도체 규격을 유지하며 팬아웃 공정으로 전환이 가능해 신규 인증 부담도 낮출 수 있다고 회사는 설명했다. 네패스라웨는 차량용 마이크로컨트롤러유닛 (MCU)와 같이 생산량이 많고 전방 고객 인증이 까다로운 제품에 적용시 제조과 품질 관리 경쟁력을 확보할 수 있을 것으로 기대했다.

네패스라웨는 이번 샘플 공급을 시작으로 모바일 이외에 산업용, 자동차 등 다양한 응용제품에 FO-PLP 기술을 적용, 고객 저변을 확대할 방침이다. 회사 관계자는 “팬아웃 몰딩 기술 상용화로 첨단 패키지 시장에서 기술 경쟁력을 한 층 더 강화할 수 있게 될 것”이라고 밝혔다.